摘 要: 介绍了3DES" title="3DES">3DES加密算法的原理并详尽描述了该算法的FPGA设计实现。采用了状态机和流水线技术" title="状态机和流水线技术">状态机和流水线技术,使得在面积和速度上达到最佳优化;添加了输入和输出接口" title="输出接口">输出接口的设计以增强该算法应用的灵活性。各模块均用硬件描述语言" title="硬件描述语言">硬件描述语言实现,最终下载到FPGA芯片Stratix EP1S25F780C5中。

关键词: 状态机 流水线 3DES FPGA

随着网络的快速发展,信息安全越来越引起人们的关注。加密技术作为信息安全的利器,正发挥着重大的作用。通过在硬件设备(如路由器、交换机等)中添加解密功能,可使存储和传输的数据具有较高的安全性。传统的加密工作是通过在主机上运行加密软件实现的。这种方法除占用主机资源外,其运算速度较硬件加密" title="硬件加密">硬件加密要慢,密钥以明文的方式存储在程序中,或者以加密的方式存储在文件或数据库中,重要数据(如个人密码PIN等)会在某一时刻以明文形式出现在计算机的内存或磁盘中,安全性较差。而硬件加密是通过独立于主机系统外的硬件加密设备实现的,所有关键数据的存储、运算都通过硬件实现,不占主机资源、速度快、安全性较高。

尽管DES已被证实是不安全的算法(主要是密钥太短),但三重DES增加了密钥长度,由56位增加到112或168位,有更高的安全性,而且在新一代因特网安全标准IPSEC协议集中已将DES作为加密标准。另一方面,基于DES算法的加/解密硬件目前已广泛应用于国内外卫星通信、网关服务器、机顶盒、视频传输以及其它大量的数据传输业务中。利用3DES可以使原系统不作大的改动。所以对3DES的研究仍有很大的现实意义。

1 3DES加密算法描述

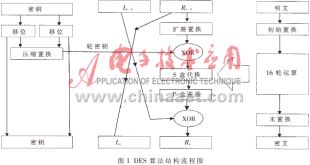

DES成为一个世界范围内的标准已经20多年了,很好地抗住了多年的密码分析,除最强有力的可能敌手外,对其它的攻击仍是安全的。DES对64位的明文分组进行操作,通过一个初始置换,将明文分成左半部分和右半部分,然后进行16轮完全相同的运算,最后经过一个末置换便得到64位密文。每一轮的运算包含扩展置换、S盒代换、P盒置换和两次异或运算,另外每一轮中还有一个轮密钥(子密钥)。整体框图如图1所示。

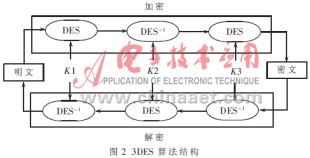

3DES(即Triple DES)是DES向AES过渡的加密算法(1999年,NIST将3-DES指定为过渡的加密标准),是DES的一个更安全的变形。它以 DES为基本模块,通过组合分组方法设计出分组加密算法。其具体实现如下:设Ek()和Dk()代表DES算法的加密和解密过程,K代表DES算法使用的密钥,P代表明文,C代表密文。这样,

3DES加密过程为:C=Ek3(Dk2(Ekl(P)))

3DES解密过程为:P=Dkl(Ek2(DK3(C)))

具体的加/解密过程如图2所示。K1、K2、K3决定了算法的安全性,若三个密钥互不相同,本质上就相当于用一个长为168位的密钥进行加密。多年来,它在对付强力攻击时是比较安全的。若数据对安全性要求不那么高,K1可以等于K3。在这种情况下,密钥的有效长度为112位。

2 FPGA设计实现

2.1 FPGA设计的优势

用硬件实现某种密码算法,首先要用硬件描述语言(如VHDL、Verilog HDL)进行系统设计和编码,然后采用专用集成电路(ASIC)或现场可编程逻辑门阵列(FPGA)来具体实现。采用ASIC方法设计周期较长,且费用也较昂贵;而采用FPGA,可由设计者自己对芯片内部单元进行配置,设计比较灵活,只需改变配置就可实现完全不同的功能,大大缩短了设计周期和开发时间,节省人力物力,同时经过优化可以达到较高的性能。另外,有多种EDA开发软件支持FPGA的设计,在本设计中作者采用了ALTERA公司的QuartusⅡ开发软件。

2.2 状态机和流水线技术的应用

面积和速度这两个指标贯穿着FPGA设计的始终,是设计质量评价的终极标准。设计目标就是在满足给定的时序要求(包含对设计频率的要求)的前提下,占用较小的芯片面积;或者在所规定的面积下,使设计时序余量更大,频率更高。通过功能模块复用可减少设计消耗的芯片面积;反之,并行复制多个操作模块可较大地提高设计频率。在本设计中充分考虑了这一对矛盾体,采用状态机和流水线相结合的技术,使得在减少芯片资源消耗的情况下又能提高设计频率。

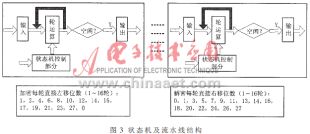

状态机是组合逻辑和寄存器逻辑的特殊组合,尤其适合于数字系统的控制设计。系统的状态在一定的条件下相互转移。分析DES的算法结构可以发现,轮运算是相同的,只是输入子密钥不同,同时各轮的子密钥都可以通过密钥移位再经过一个压缩置换操作直接得到,所以将轮运算作为一个共享模块,反复进行该操作,其输入参数由状态机控制部分提供,主要是密钥移位的位数。只在空闲状态下将轮运算结果输出。因数据端是16位,故每个状态机模块中进行四轮轮运算。

流水线处理是高速设计中的一个常用设计手段。如果某个设计的处理流程可分为若干步骤,而且整个数据处理是“单流向”的,即没有反馈,前一个步骤的输出是下一个步骤的输入,则可以考虑用流水线设计方法提高系统的工作频率。流水线设计是一种技巧,它在很长组合路径的中间点引入寄存器。寄存器会增加等待时间,但却能增加速度,减少逻辑级。此外,附加寄存器虽然会增加一定的功耗,但却极大地减少了毛刺。流水线处理方式之所以频率较高,是因为复制了处理模块,它是FPGA设计中面积换取速度思想的具体体现。DES的16轮运算结构是相同的,符合流水线设计的要求,所以基于DES的结构特点,将前面的状态机模块作为流水线的一个单元,这样DES共有四个单元,串联起来形成四级流水线。因状态机中有寄存器,能保证流水线的工作,所以各单元间不需再加寄存器。状态机及流水线结构如图3所示,图中给出了由密钥直接生成各子密钥的移位数。将DES模块复制三份,就形成了16级流水线,所不同的是流水线内部是状态机结构,所以每四个时钟周期才会得到一组加/解密结果。这种结构同样适用于数据端是8位和32位的。

2.3 S盒的设计和接口设计

在3DES算法中,S盒代替是算法的关键所在。其它的运算都是线性的,易于分析和实现,而S盒是非线性的,因此S盒的设计和优化将直接影响整个系统的性能。DES的8个S盒都是6输入、4输出的结构,适合于用ROM来实现,因此用VHDL定义如下结构设计的ROM:

input : in std_logic_vector(5 downto 0);

output : out std_logic_vector(3 downto 0);

subtype s_word is std_logic_vector(3 downto 0);

subtype s1_rangeij is integer range 0 to 63;

type s_type is array(s1_rangeij) of s_word;

constant s:s_type:=( (“1110”),(“0100”),(“1101”),(“0001”)……);

function logic2int(din:std_logic_vector(5 downto 0)) return s1_rangeij --二进制转换为十进制

output<=s(logic2int(input));

经综合后,每个S盒只用了24个逻辑单元。

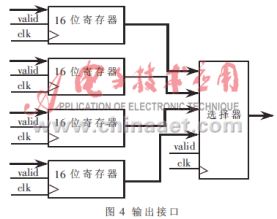

3DES是64位分组大小的加密算法,数据线一般是8位、16位或32位,为此增加了输入、输出接口,这部分接口完成的功能就是串/并转换和并/串转换。以16位输出接口为例,设计中将加/解密出来的数据从低位到高位在valid信号有效的情况下同时存入四个16位寄存器,再通过一个选择器依次将数据送出。该选择器不同于普通的多路选择器,它是由valid信号触发其内的计数功能,从而依次将寄存器中数据输出,如图4所示。输入接口要简单一些,只需一个64位可移位的寄存器,在第四个16位数据到来后才将这一组64位数据送给加密模块。这种结构非常容易用硬件描述语言实现。

2.4 总体结构

通过一个密钥控制模块为3DES提供三个56位的密钥以及加/解密控制信号。密钥的输入是28位的,所产生的三个56位密钥并不是同一时间提供给3DES的,相互之间有16个时钟的延时,这样可以保证修改密钥后并不影响先前流水线的工作。再加上输入、输出接口就构成了该设计的总体结构,如图5所示。限于图的大小,不影响理解的部分信号没有画出。加/解密的流程是先输入六组28位的密钥,然后就可以发送需要加/解密的数据了,中间可以有间断,如果需要更改密钥,也是先输入改后的密钥,再输入数据,可实时更改,无需等到流水线中最后一组数据加/解密完成。

本设计在ALTERA公司的QuartusⅡ环境下用VHDL、Verilog HDL实现设计输入,采用同步时钟,成功编译、综合、适配和仿真,并下载到Stratix系列FPGA芯片EP1S25F780C5中。在综合的过程中用逻辑锁等技术进行了优化。消耗逻辑单元16250个,设计时钟频率可达95.07MHz。

参考文献

1吴世忠.应用密码学[M].北京:机械工业出版社,2003

2潘 松,黄继业.EDA技术实用教程.北京:科学出版社,2003